Now that I have my factory running and producing everything in high volume, I decided to experiment with the game mechanics to form binary logic gates and perform math operations.

This is what I came up with:

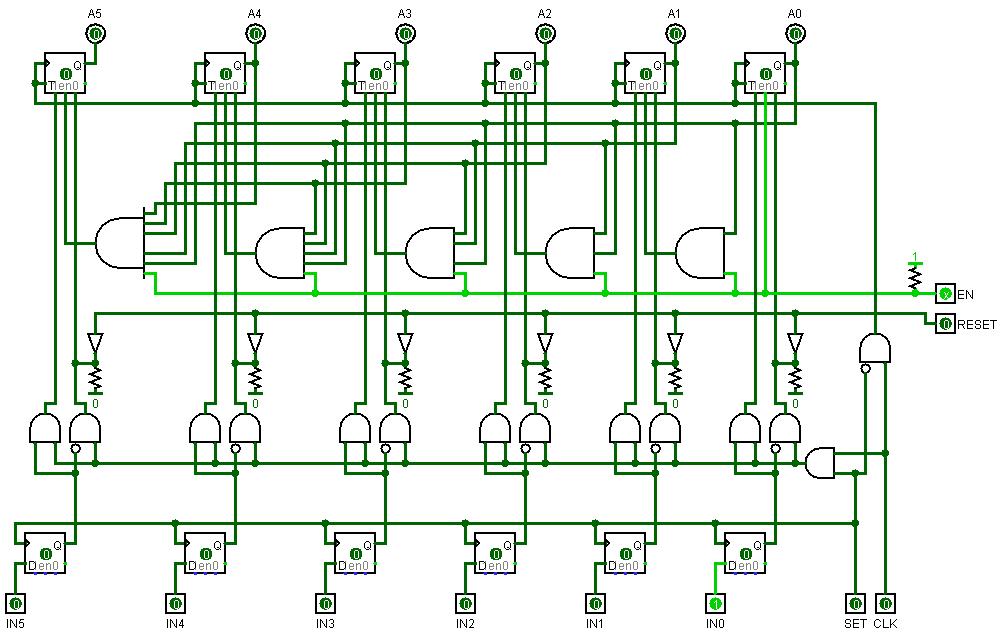

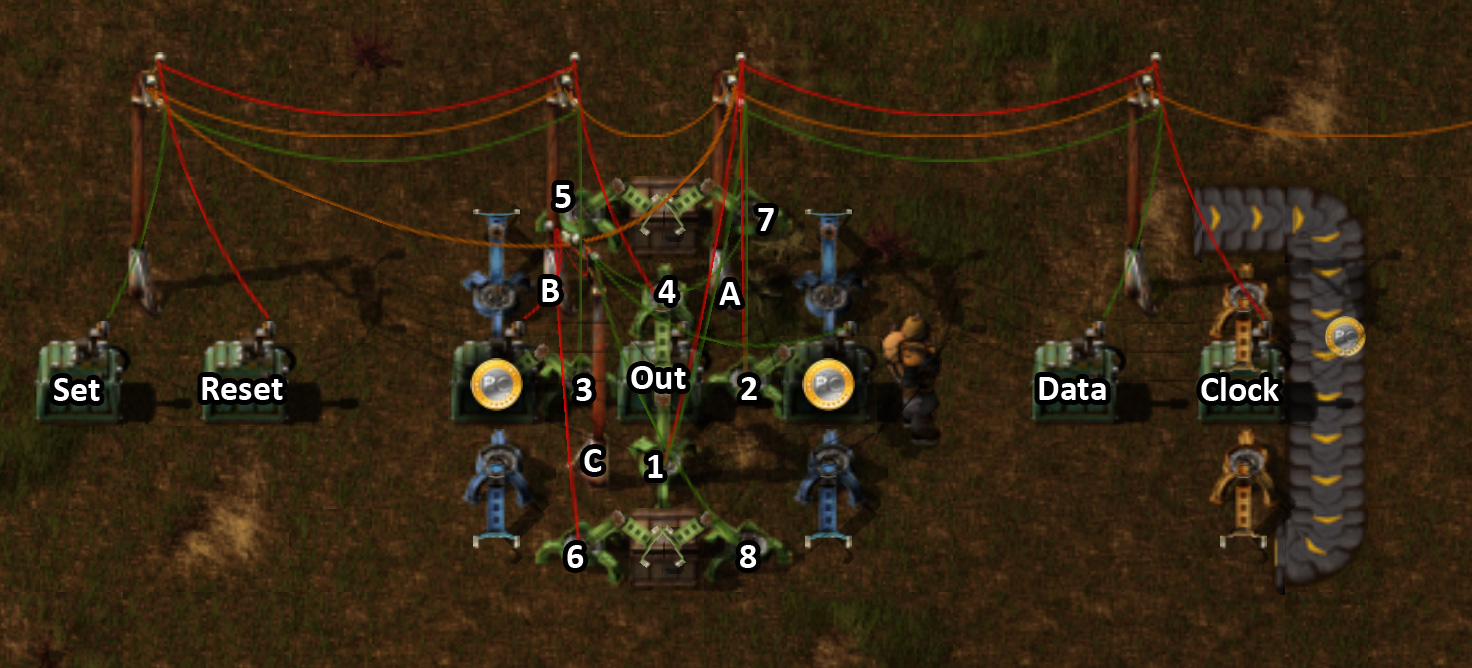

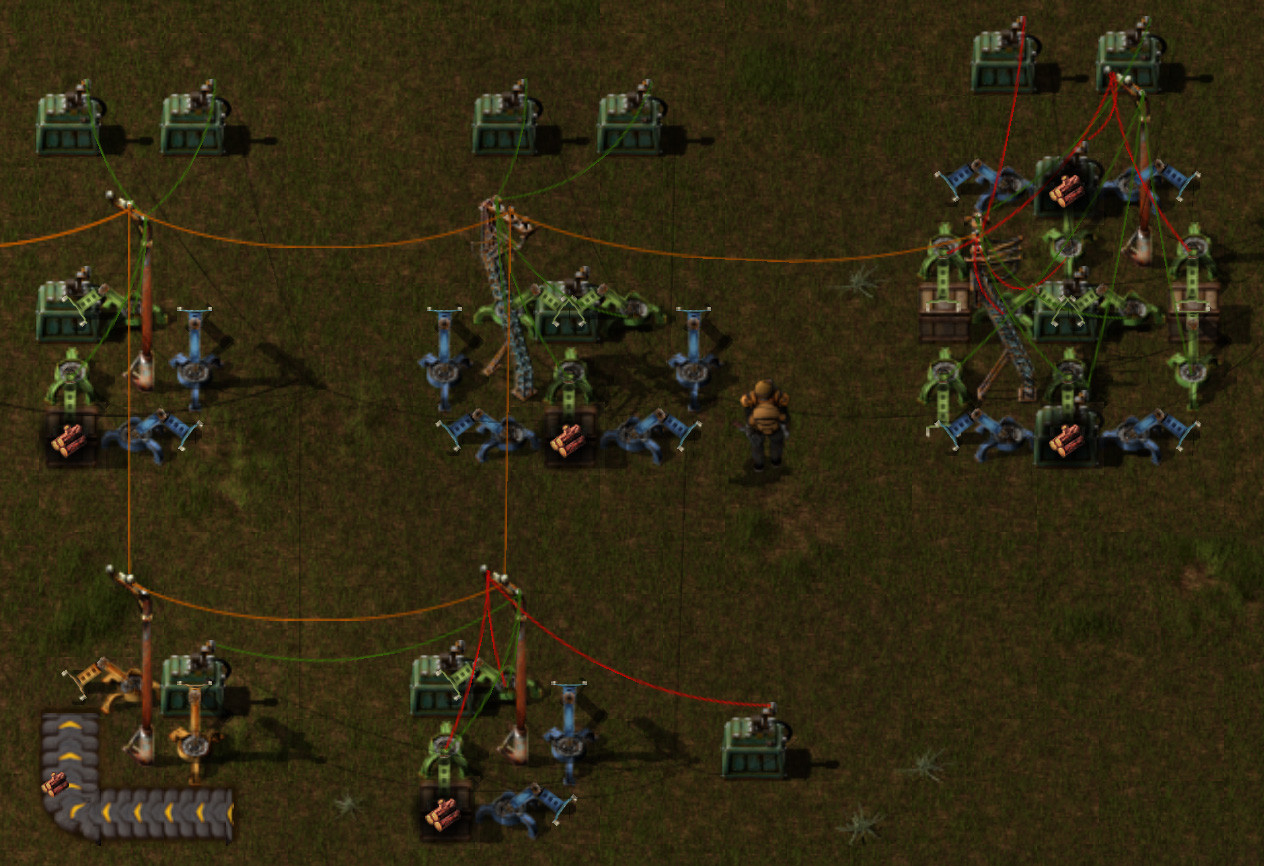

These are my basic cell arrangements to form the binary gates (AND, OR, NOT, XOR, Flip Flops, ...) by adjusting the circuit network wiring/smart inserter rules, which are then used in combination to perform more complex binary operations.

Full album with some description: http://imgur.com/a/tZ2HB#0

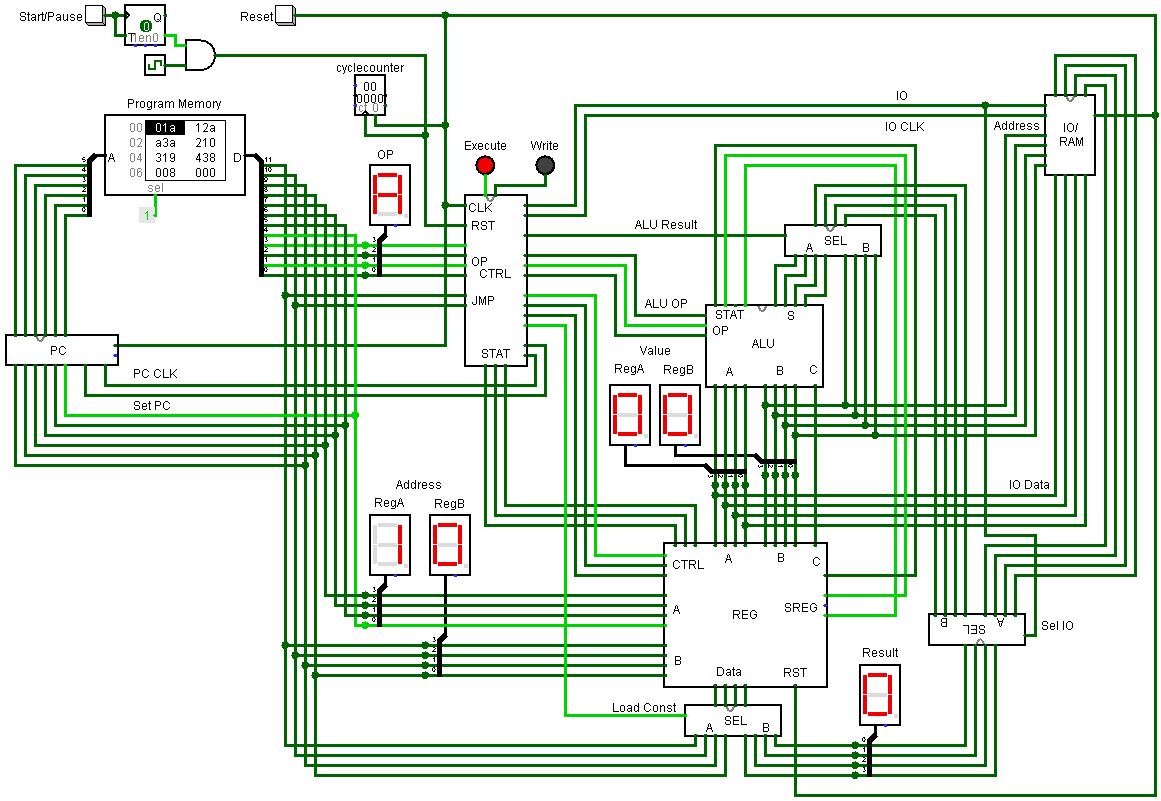

In the album you can already see some bigger arrangements which I want to use to build a simple 4-bit CPU (more a sort of a microcontroller, it will also have the program- and data memories and some peripherals), lets see